總攬

https://myfamily12345.pixnet.net/blog/post/404540683

PCI

http://myfamily12345.pixnet.net/blog/post/403329224-PCI%E3%80%81PCI-X%E3%80%81PCIe%E4%BB%8B%E7%B4%B9

http://myfamily12345.pixnet.net/blog/post/403331330-linux%20for%20PCIe

SATA 架構與資料

https://myfamily12345.pixnet.net/blog/post/404543587-sata

PCIe Fabric Terminology

- Root Complex (RC)

: It is a PCIe host. It usually provides slots using which other PCI / PCIe devices can be connected. - End Point (EP)

: It is a PCIe device which usually has peripherals like USB or SATA. It has its own address space (32b/64b). - Bridge: A Bridge is used to connect a PCI/PCIX device to a PCIe root complex.

- Switch: A switch is used to connect multiple PCI Express devices to the root complex. If there are no enough slots

in the board a switch will be used.

PCI Express 架構

實體層

基礎實體層 (physical layer) 包含 2 個單工通道

如圖 所示,PCI Express 的基本連結包含 2 組低電壓的 AC 偶合差動訊號對 (傳送對與接收對各 1 組)。實際的連結訊號則使用解加強 (de-emphasis) 方式,以降低符元干擾 (Intersymbol Interference,ISI),並提升資料品質。嵌入的資料時脈為 8b/10b 編碼基模,可達到極高的資料傳輸率。各個方向的訊號初始頻率為 2.5 Gb/s (產生 1 組訊號),且可隨著更先進的晶片技術進一步讓各個方向的傳輸率達到 10 Gb/s (銅線訊號的實際最大值)。 實體層將於 2 組 PCI Express 代理程式之間傳輸封包

PCI Express 連結頻寬可新增訊號組合來構成多個 Lane,達到線性調整目的。實體層具備 x1、x2、x4、x8、x12、x16 與 x32 的 Lane 寬度,概念上可於這些 Lane 之間切割進入系統的資料封包。透過 8b/10b 編碼功能,每個位元組就可以在各個 lane 之間進行傳輸。對其他層級而言,資料的重組或解組 (disassembly) 都不需再額外進行處理。在初始化作業期間,各個連結末端的 2 組代理程式將就 Lane 寬度與作業頻率相互協調,以設定各組 PCI Express 連結。此時尚未牽涉任何韌體或作業系統軟體。PCI Express 架構可透過速度升級與高階編碼技術,提升日後相關效能的表現。 未來的系統速度、編碼技術或媒體,僅會影響實體層。

若要於 PCI Express 中使用不同的 Lane 寬度,則使用者必須注意擴充介面卡所需的寬度,使其符合主機板本身的 Lane 寬度。除了繪圖卡可能需要 x16 的 Lane 寬度之外,大多數的 PCI Express 擴充卡目前都使用 x1 的寬度。 若需要更高頻寬,則可使用更多組需要較高頻寬的介面卡。根據目前市場對電腦需求的不同,x1、x4、x8 與 x16 插槽的組合也有所不同。依失配 (mismatch) 方向的不同,PCI Express 可容許失配 Lane 寬度之間具有一些可互通性 (interoperability)。若於較低頻寬接頭中使用較高頻寬的擴充卡,就是所謂的「縮減插頭」(down-plugging)。以 PCI 匯流排為例,可將 64 位元的介面卡插入至 32 位元的插槽中。

有RS-232介面的PCIe x1卡

與 PCI 相比較, PCI Express 規格特別設計擴充卡與接頭,以避免縮減插頭的需要。另一種失配是,在較高頻寬的接頭中使用較低頻寬的擴充卡,就是所謂的「擴充插頭」(up-plugging)。主機板製造商必須提供警示說明,提醒使用者「擴充插頭」僅可支援 1 組 x1 資料傳輸率的擴充卡,即使擴充卡具備較高傳輸率,為提升傳輸率所做的相關投資將可能無法發揮效益。不論特定主機板是否可透過完整的資料傳輸率來處理擴充插頭設定中的擴充卡,使用者都必須根據不同情況,逐一對主機板製造商進行確認。舉例來說,若將某幾款主機板插入至 x8 或 x16 插槽時,可用完整的 x4 資料傳輸率來操作 x4 擴充卡;但是相同製造商的他款主機板,卻可能僅以 x1 執行擴充卡。 如果主機板同時具備 1 組整合式 (內建) 繪圖控制器,與 1 組 x16 PCI Express 插槽可擴充繪圖功能,則當啟動內建繪圖功能時,往往無法同時使用該 x16 插槽。

資料連結層 (link layer)

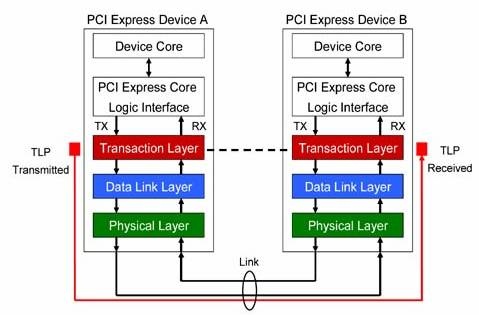

連結層的主要功能,是為了穩定 PCI Express 連結的封包傳輸。如圖 所示,連結層負責資料品質,並將序號與 CRC 新增至傳輸層封包。大多數封包皆於傳輸層中進行初始化。信用架構 (credit-based) 的流量控制協定,可確保在有可用緩衝區時才進行封包傳輸,以於另一端接收該筆封包。如此可降低因資源限制所造成的封包重傳與匯流排頻寬浪費。 當封包訊號出現損毀情況時,連結層將自動重新傳輸。

Sequence Number: It's the targeted ID/ start ID of a target (Address routing, ID routing, Implicit routing)

LCRC: It is used for DLLP data integrity protection. These are generated by switches (3-port virtual bridge device contains memory, I/O, registers). Remaining Header, Data Payload, ECRC is the TLLP. This layer consists of Data link control & management state (DLCMSM) mechanism to perform tasks.

傳輸層 (transaction layer)

傳輸層可接收軟體層的讀取與寫入請求,再建立請求封包以傳輸至連結層。所有請求都以分割式資料交易方式來實作,且某些請求封包會要求回應封包 (response packet)。傳輸層也可接收連結層的回應封包,並與原始的軟體請求進行比對。各組封包均具有專屬的辨識碼,得以將回應封包導向正確的源頭。封包格式為 32 位元的記憶體定址 (addressing),也有擴充的 64 位元記憶體定址。 封包也具備「no-snoop」、「relaxed ordering」與「priority」的屬性,可將封包引導至最佳的 I/O 子系統。

- Header: Indicates type of Transactions (Memory read, Memory write etc)

- Data Payload: This is the data that is to be sent

- ECRC: This is used to detect errors in TLPs

TLP Transaction Types

Communication is done through Transaction layer packets (TLP). These transactions are of four types.

- Memory Read/Write (Mrd/MWr): These are used to transfer data from/to the mapped memory location

- IO Read/Write(IORd/IOWr): These are used to transfer data from/to I/O location

- Configuration Read/Write(CfgRd/CfgWr): These are used to configuring the end points

- Message Transaction: These are used for signaling an event and general messaging. Supports Vendor defined messages

傳輸層具備 4 組定址空間 – 包括 3 組 PCI 定址空間 (記憶體、I/O,與組態) 與 1 組訊息空間。PCI 2.2 則提供了傳播系統中斷的替代方式,就是所謂的訊息式中斷 (MSI)。此處是使用特定格式的記憶體寫入傳輸方式,以取代 PCI 2.2 系統中的硬接線式邊帶訊號 (hard-wired sideband signal) 功能。PCI Express 規格則再使用 MSI 概念,做為中斷處理的主要方式,並透過訊息空間接收先前所有的邊帶訊號與帶內 (in-band) 訊息,如中斷 (interrupt)、電力管理請求與重設 (reset)。PCI 2.2 規格中的其他「特殊週期」,如中斷認知 (interrupt acknowledge),也屬於帶內訊息。 對平台建置所使用的邊帶訊號而言,由於 PCI Express 訊息可將邊帶訊號的陣列降至最低,因此可將 PCI Express 訊息假想為「虛擬接線」。

軟體層 (software layer)

PCI Express 的軟體相容性至關重要。軟體相容性主要分為 2 項:初始化或列舉 (enumeration) 與執行時間 (run time)。PCI 具備強大的初始化模式,讓作業系統可找出所有的附加硬體裝置,接著可分配系統資源 (如記憶體、I/O 空間與中斷),藉以建立理想的系統環境。 PCI 組態空間與 I/O 裝置的可程式化性,是 PCI Express 架構中維持不變的關鍵要素;事實上,不需針對 PCI Express 架構的機器進行修改,所有的作業系統都可開機。PCI 所使用的執行時間軟體模式屬於載入儲存 (load-store) 的共用記憶體模式,PCI Express 架構沿用此運作模式讓現有軟體可依原樣繼續執行。 新款軟體也可利用某幾項 PCI Express 的高階功能,像是此篇技術文件未提到的進階切換。

UNDERSTANDING THE PCIE PACKET FLOW

The root complex can directly access the memory without CPU intervention just like DMA. PCIe device can also use the same feature to read/write. The host should give permission to access the memory and know the address into which the data should be read/written. Root complex allows other devices to be connected using root ports. In the figure1, three root ports are used.

The host system can access the PCIe endpoint only using the PCIe address space. This address space is a virtual address space for which no physical memory is allocated. It is just like a list of addresses used in the Transaction Layer Packet in order to identify the target of the packet.

Root complex has IP registers in order to configure the IP. It has registers to enable the clocks, to program the file, to configure the lane width (1 lane or 2 lane), configure the speed mode (gen 1 or gen2 or gen3). It has registers to translate address from CPU address to PCIe address.

Configurable address space is used by the CPU in order to access the PCIe address space. There are four spaces in a PCIe system: memory space, IO space, message space and configuration space. Apart from message space all others will have physical address associated with it. The size of the configuration space is 4KB while that of an IO space is 64KB.Configuration space will have all the information about the device. It has device ID, vendor ID, class code and various capabilities of the device. It is a software backward compatible to a PCI which has a size of 250Bytes. Of this 4KB of configuration space, the first 64 bytes are standard and are called as Standardized Headers.

These Standardized Headers are of two types (Type 0 & Type 1) .Type 0 will be used by the PCIe end points and will have information that is applicable to end points. Type 1 will be used by root ports, bridges and switches. It contains information applicable only to those. Every PCIe end point will also have a configuration space just that it has different type of header that is used in root complex.

During the Enumeration process the host system should read the configuration space of the end point, this has to be mapped to some address in the PCIe address space. The mechanism in which the PCIe end point maps to the address space is called as the Enhanced Configuration Access.

In the Base Address Register, the last bit which indicates memory request or I/O request if it is 0 or 1, and the next two bits indicates whether 32 bit or 64 bit address decoding, the next bit indicates whether the memory is pre-fetchable or non Pre- fetchable.

In order to access the configuration space of PCIe end point from PCIe address space, the host uses the configurable address space in the Root Complex. A size of 4kb is allocated since the configuration space can only be of size 4kb. This region in the configurable address space should be mapped to PCIe address space by using Address Translation Table in the Root Complex IP.

在lnux 下, 查詢 PCIe device, 可以使用 lspci

在lnux 下, 查詢 PCIe device, 可以使用 lspci

PCI 的裝置使用三個編號用來當作識別值,個別為

1.匯流排(bus number), 2. 裝置(device number) 以及 3. 功能(function number).

當同一各裝置上,具有一個以上功能時,function number 會大於一

03:00.0 是 PCIe 介面的SSD

所以剛剛的 03:00.0 就是 bus number = 03 ,device number = 00 function = 0 .

這3個編號會組合成一個 16-bits 的識別碼,

- 匯流排(bus number) 8bits 2^8 至多可連接 256 個匯流排(0 to ff),

- 裝置(device number) 5bits 2^5 至多可接 32 種裝置(0 to 1f) 以及

- 功能(function number) 3bits 2^3 至多每種裝置可有 8 項功能(0 to 7).

或是用 lspci -vvv -s 查詢更詳細的資訊

參考資料:

https://isite.tw/2016/06/20/16031

http://www.ni.com/white-paper/3767/zht/

https://zh.wikipedia.org/wiki/PCI_Express

http://www.sionsemi.com/whitepapers/pcie-overview.html

http://pinouts.ru/Slots/pci_express_pinout.shtml

留言列表

留言列表